HOST主桥的实现因处理器系统而异。PowerPC处理器和x86处理器的HOST主桥除了集成方式不同之外,其实现机制也有较大差异。但是这些HOST主桥所完成的最基本功能依然是分离存储器域与PCI总线域,完成PCI总线域到存储器域,存储器域到PCI总线域之间的数据传递,并管理PCI设备的配置空间。

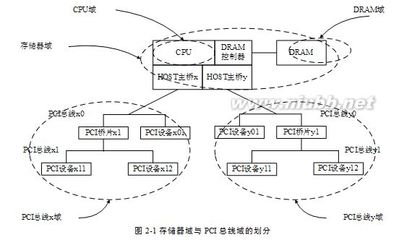

上文曾经多次提到在一个处理器系统中,存在PCI总线域与存储器域,深入理解这两个域的区别是理解HOST主桥的关键所在。在一个处理器系统中,存储器域、PCI总线域与HOST主桥的关系如图2‑1所示。

上图所示的处理器系统由一个CPU,一个DRAM控制器和两个HOST主桥组成。在这个处理器系统中,包含CPU域、DRAM域、存储器域和PCI总线域地址空间。其中HOST主桥x和HOST主桥y分别管理PCI总线x域与PCI总线y域。PCI设备访问存储器域时,也需要通过HOST主桥,并由HOST主桥进行PCI总线域到存储器域的地址转换;CPU访问PCI设备时,同样需要通过HOST主桥进行存储器域到PCI总线域的地址转换。

如果HOST主桥支持Peer-to-Peer传送机制,PCI总线x域上的设备可以与PCI总线y域上的设备直接通信,如PCI设备x11可以直接与PCI设备y11通信。为简化模型,在本书中,PCI总线仅使用32位地址空间。

2.1.1CPU域、DRAM域与存储器域

CPU域地址空间指CPU所能直接访问的地址空间集合。在本书中,CPU、处理器与处理器系统的概念不同。如MPC8548处理器的内核是E500 V2[1],本书将这个处理器内核称为CPU;处理器由一个或者多个CPU、外部Cache、中断控制器和DRAM控制器组成;而处理器系统由一个或者多个处理器和外部设备组成。

在CPU域中有一个重要概念,即CPU域边界,所谓CPU域边界,即CPU所能控制的数据完整性边界。CPU域的边界由Memory Fence指令[2]的作用范围确定,CPU域边界的划分对数据完整性(Data Consistency)非常重要。与CPU域相关的数据完整性知识较为复杂,可以独立出书,因此本篇对数据完整性不做进一步介绍。笔者有计划再更新完PCIe总线部分的资料后,书体系结构的两方面内容,一个是Cache层次结构,一个是以Weakly Ordered Memory Modle为基础书写数据完整性。

严格的讲CPU域仅在CPU内核中有效,CPU访问主存储器时,首先将读写命令放入读写指令缓冲中,然后将这个命令发送到DRAM控制器或者HOST主桥。DRAM控制器或者HOST主桥将CPU地址转换为DRAM或者PCI总线地址,分别进入DRAM域或者PCI总线域后,再访问相应的地址空间。

DRAM域地址空间指DRAM控制器所能访问的地址空间集合。目前处理器系统的DRAM一般由DDR-SDRAM组成,有的书籍也将这部分内存称为主存储器。在有些处理器系统中,DRAM控制器能够访问的地址空间,并不能被处理器访问,因此在这类处理器系统中,CPU域与DRAM域地址空间并不等同。

比如有些CPU可以支持36位的物理地址,而有些DRAM控制器仅支持32位的物理地址,此时CPU域包含的地址空间大于DRAM域地址空间。但是这并不意味着DRAM域一定包含在CPU域中,在某些处理器系统中,CPU并不能访问在DRAM域中的某些数据区域。而CPU域中除了包含DRAM域外,还包含外部设备空间。

在多数处理器系统中,DRAM域空间是CPU域空间的一部分,但是也有例外。比如显卡控制器可能会借用一部分主存储器空间,这些被借用的空间不能被CPU访问,而只能被DRAM控制器,更为准确地说是显卡通过DRAM控制器访问,因此这段空间不属于CPU域,严格地讲,这段空间属于外部设备域。

本书使用存储器域统称CPU域与DRAM域。存储器域包括CPU内部的通用寄存器,存储器映像寻址的寄存器,主存储器空间和外部设备空间。在Intel的x86处理器系统中,外部设备空间与PCI总线域地址空间等效,因为在x86处理器系统中,使用PCI总线统一管理全部外部设备。为简化起见,本书使用PCI总线域替代外部设备域。

值得注意的是,存储器域的外部设备空间,在PCI总线域中还有一个地址映射。当处理器访问PCI设备时,首先访问的是这个设备在存储器域上的PCI设备空间,之后HOST主桥将这个存储器域的PCI总线地址转换为PCI总线域的物理地址[3],然后再通过PCI总线事务访问PCI总线域的地址空间。

2.1.2PCI总线域

在x86处理器系统中,PCI总线域是外部设备域的重要组成部分。实际上在Intel的x86处理器系统中,所有的外部设备都使用PCI总线管理。而AMD的x86处理器系统中还存在一条HT(HyperTransport)总线,在AMD的x86处理器系统中还存在HT总线域。本书对HT总线不做进一步介绍。

PCI总线域(PCI Segment)由PCI设备所能直接访问的地址空间组成。在一个处理器系统中,可能存在多个HOST主桥,因此也存在多个PCI总线域。如在图2‑1所示的处理器系统中,具有两个HOST主桥,因而在这个处理器系统中存在PCI总线x和y域。

在多数处理器系统中,分属于两个PCI总线域的PCI设备并不能直接进行数据交换,而需要通过FSB进行数据交换。值得注意的是,如果某些处理器的HOST主桥支持Peer-to-Peer数据传送,那么这个HOST主桥可以支持不同PCI总线域间的数据传送。

PowerPC处理器使用了OCeaN技术连接两个HOST主桥,OCeaN可以将属于x域的PCI数据请求转发到y域,OCeaN支持PCI总线的Peer-to-Peer数据传送。有关OCeaN技术的详细说明见第2.2节。

2.1.3处理器域

处理器域是指一个处理器系统能够访问的地址空间集合。处理器系统能够访问的地址空间由存储器域和外部设备域组成。其中存储器域地址空间较为简单,而在不同的处理器系统中,外部设备域的组成结构并不相同。如在x86处理器系统中,外部设备域主要由PCI总线域组成,因为大多数外部设备都是挂接在PCI总线[4]上的,而在PowerPC处理器和其他处理器系统中,有相当多的设备与FSB直接相连,而不与PCI总线相连。

本书仅介绍PCI总线域而不对其他外部设备域进行说明。其中存储器域与PCI总线域之间由HOST主桥联系在一起。深入理解这些域的关系是深入理解PCI体系结构的关键所在,实际上这也是理解处理器体系结构的基础。

通过HOST主桥,处理器系统可以将处理器域划分为存储器域与PCI总线域。其中存储器域与PCI总线域,彼此独立,并通过HOST主桥进行数据交换。HOST主桥是联系存储器域与PCI总线域的桥梁,是PCI总线域实际的管理者。

有些书籍认为HOST处理器是PCI总线域的管理者,这种说法并不精确。假设在一个SMP(symmetricmultiprocessing)处理器系统中,存在4个CPU而只有一个HOST主桥,这4个CPU将无法判断究竟谁是HOST处理器。不过究竟是哪个处理器作为HOST处理器并不重要,因为在一个处理器系统中,是HOST主桥管理PCI总线域,而不是HOST处理器。当一个处理器系统中含有多个CPU时,如果这些CPU都可以访问HOST主桥,那么这些CPU都可以作为这个HOST主桥所管理PCI总线树的HOST处理器。

在一个处理器系统中,CPU所能访问的PCI总线地址一定在存储器域中具有地址映射;而PCI设备能访问的存储器域的地址也一定在PCI总线域中具有地址映射。当CPU访问PCI域地址空间时,首先访问存储器域的地址空间,然后经过HOST主桥转换为PCI总线域的地址,再通过PCI总线事务进行数据访问。而当PCI设备访问主存储器时,首先通过PCI总线事务访问PCI总线域的地址空间,然后经过HOST主桥转换为存储器域的地址后,再对这些空间进行数据访问。

由此可见,存储器域与PCI总线域的转换关系由HOST主桥统一进行管理。有些处理器提供了一些寄存器进行这种地址映射,如PowerPC处理器使用Inbound和Outbound寄存器组保存存储器域与PCI总线域的地址映射关系;而有些处理器并没有提供这些寄存器,但是存储器域到PCI总线域的转换关系依然存在。

HOST主桥进行不同地址域间的数据交换时,需要遵循以下规则。为区别存储器域到PCI总线域的地址映射,下文将PCI总线域到存储器域的地址映射称为反向映射。

(1)处理器访问PCI总线域地址空间时,首先需要访问存储器域的地址空间,之后通过HOST主桥将存储器地址转换为PCI总线地址,之后才能进入PCI总线域进行数据交换。PCI设备使用的地址空间保存在各自的PCI配置寄存器中,即BAR寄存器中。这些PCI总线地址空间需要在初始化时映射成为存储器域的存储器地址空间,之后处理器才能访问这些地址空间。在有些处理器的HOST主桥中,具有独立的寄存器保存这个地址映射规则,如PowerPC处理器的Outbound寄存器组;而有些处理器,如在x86处理器中,虽然没有这样的寄存器组,但是在HOST主桥的硬件逻辑中仍然存在这个地址转换的概念。

(2)PCI设备访问存储器域时,首先需要访问PCI总线域的地址空间,之后通过HOST主桥将PCI总线地址转换为存储器地址,之后才能穿越HOST主桥进行数据交换。为此处理器需要通过HOST主桥将这个PCI总线地址反向映射为存储器地址。PCI设备不能访问在PCI总线域中没有进行这种反向映射的存储器域地址空间。PowerPC处理器使用Inbound寄存器组存放PCI设备所能访问的存储器空间,而在x86处理器中并没有这样的寄存器组,但是依然存在这个地址转换的概念。

(3)如果HOST主桥不支持Peer-to-Peer传送方式,那么分属不同PCI总线域的PCI设备间不能直接进行数据交换。在32位的PCI总线中,每一个PCI总线域的地址范围都是0x0000-0000~0xFFFF-FFFF,但是这些地址没有直接联系。PCI总线x域上的PCI总线地址0x0000-0000与PCI总线y域上的PCI总线地址0x0000-0000并不相同,而且这两个PCI总线地址经过HOST主桥反向映射后,得到的存储器地址也不相同。

本篇在第2.2节中,主要以PowerPC处理器为例说明HOST主桥的实现机制,并在第2.2.4节简要说明了x86处理器中的南北桥构架。尽管部分读者对PowerPC处理器并不感兴趣,笔者仍然强烈建议读者仔细阅读第2.2节的全部内容。

在PowerPC处理器中,HOST主桥的实现比较完整,尤其是PCI总线域与存储器域的映射关系比较明晰,便于读者准确掌握这个重要的概念。而x86处理器由于考虑向前兼容,设计中包含了太多的不得已,x86处理器有时不得不保留原设计中的不完美,向前兼容是Intel的重要成就,也是一个沉重的十字架。

[1] MPC8548处理器基于E500 V2内核。目前E500内核包括V1,V2和mc(MultiCore)三个版本。

[2] x86处理器的Memory Fence指令为MFENCE,LFENCE和SFENCE,而PowerPC处理器的Memory Fence指令为msync和mbar。

[3] PCI总线域只含有物理地址,因此下文将直接使用PCI总线地址,而不使用PCI总线物理地址。

[4] AMD的x86处理器中的某些外部设备,可能是基于HT总线,而不使用PCI总线。

爱华网

爱华网