1红基色 red

2绿基色 green

3蓝基色 blue

4地址码 ID Bit

5自测试 ( 各家定义不同 )

6红地

7绿地

8蓝地

9保留 ( 各家定义不同 )

10数字地

11地址码

12地址码

13行同步

14场同步

15地址码 ( 各家定义不同 )

http://www.weeqoo.com/zhuanti/VGA-Interface/

VGA接口

VAG接口设计应用VGA接口常用电路VGA接口定义

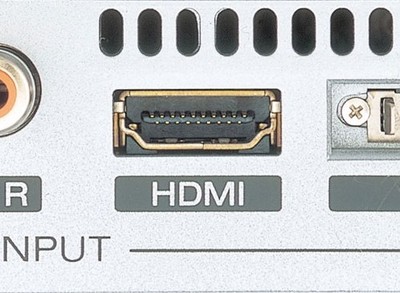

VGA接口产生原因: 显卡所处理的信息最终都要输出到显示器上,显卡的输出接口就是电脑与显示器之间的桥梁,它负责向显示器输出相应的图像信号。CRT显示器因为设计制造上的原因,只能接受模拟信号输入,这就需要显卡能输入模拟信号。VGA接口就是显卡上输出模拟信号的接口,VGA(VIDEOGraphics Array)接口,也叫D-Sub接口。虽然液晶显示器可以直接接收数字信号,但很多低端产品为了与VGA接口显卡相匹配,因而采用VGA接口。

VGA接口是一种D型接口,上面共有15针空,分成三排,每排五个。VGA接口是显卡上应用最为广泛的接口类型,多数的显卡都带有此种接口。有些不带VGA接口而带有DVI(DigitalVisual Interface数字视频接口)接口的显卡,也可以通过一个简单的转接头将DVI接口转成VGA接口,通常没有VGA接口的显卡会附赠这样的转接头。

目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机内部以数字方式生成的显示图像信息,被显卡中的数字/模拟转换器转变为R、G、B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。对于模拟显示设备,如模拟CRT显示器,信号被直接送到相应的处理电路,驱动控制显像管生成图像。而对于LCD、DLP等数字显示设备,显示设备中需配置相应的A/D(模拟/数字)转换器,将模拟信号转变为数字信号。在经过D/A和A/D2次转换后,不可避免地造成了一些图像细节的损失。VGA接口应用于CRT显示器无可厚非,但用于连接液晶之类的显示设备,则转换过程的图像损失会使显示效果略微下降。

基于DSP Builder的VGA接口设计

引言

随着电子技术的发展,VGA(视频图形阵列)接口出现在很多嵌入式平台上,用于图像信息的实时显示等

在某些情况下,设计者希望通过普通的显示器或投影仪观测FPGA内部的一些矢量信号,即把带VGA接口的显示器当作示波器使用等,这就需要对数据进行处理,使之能够在显示器上实时显示

本文基于DSPBuilder的VGA接口设计方法,对VGA接口时序和系统设计需求进行了介绍,并在硬件平台下实现一维与二维信号的显示

VGA接口标准

VGA显像原理

显示器通过光栅扫描的方式,电子束在显示屏幕上有规律地从左到右、从上到下扫描在扫描过程中,受行同步信号控制,逐点往右扫,完成一行扫描的时间倒数为行频;同时又在行同步脉冲期内回到屏幕的左端,从上往下形成一帧,在垂直方向上受场同步信号控制,完成一帧的时间倒数为场频图像的显示过程即为在电子束扫描过程中,将地址与图像的像素依次对应,每一个被寻址的像素只获得其自身的控制信息,而与周围的像素不发生干扰,从而可以显示稳定的图像

VGA接口是显示卡上输出模拟信号的接口,也叫D-Sub接口这种接口上面共有15个针孔,分成3排,每排5个,通过模拟VGA接口显示图像的工作原理,将计算机内部以数字方式生成的显示图像信息,通过显卡中的ADC转变为R、G、B三基色信号和行、场同步信号,通过电缆传输到显示设备中

VGA时序

VGA的时序包括水平时序和垂直时序,且两者都包含的时序参数有:水平(垂直)同步脉冲、水平(垂直)同步脉冲结束到有效显示数据区开始之间的宽度(后沿)、有效显示区宽度、有效数据显示区结束到水平(垂直)同步脉冲宽度开始之间的宽度(前沿)水平有效显示区宽度与垂直有效显示区宽度逻辑与的区域为可视区域,其他区域为消隐区

一行或一场的时序信息如图1所示

图1 行/场时序图

根据目前的显示器性能参数,以LG 505E为例,其最大分辨率已可达到1024×768@60Hz,水平扫描频率30kHz~54kHz,垂直扫描频率50Hz~120Hz,带宽75MHz

基于DSP Builder的VGA接口设计方法

本设计需要完成的功能包括产生VGA时序以及基于VGA接口的信号显示设计符合VGA接口标准的接口系统,在该系统下可显示一维矢量信号与二维图像信号,并体现系统的可集成性,将该接口集成到SOPC系统中

系统时钟确定

根据系统时钟计算公式:

时钟频率=(行像素数+行消隐点数)×(一场行数+消隐行数)×刷新率

对于标准的VGA接口时序640×480@60Hz而言,时钟频率为800×525×60=25.175MHz

在本设计中我们采用1024×768@60Hz的XGA显示方式,因此系统的时钟频率PixelClk=1344×806×60=64.99MHz

状态机设计

由VGA时序可设计有限状态机来完成时序信号,以本设计1024×768@60Hz为例,对于行同步信号设计四个状态,即行同步脉冲信号区(horsync)、后沿区(backporch)、数据区(video)以及前沿区(frONtporch)用计数器hcnt的值来区分各阶段信号,最大记数值为1344场同步信号也设计成如上四个状态,当完成一行的扫描后场计数器vcnt开始计数,因此一场可以有多行

VGA DAC芯片及相应信号的生成

一般的VGA DAC芯片需要输入相应的驱动信号才能工作,包括时钟信号、同步信号、有效显示区信号等系统所用DAC芯片为FMS3818,其信号包括时钟与数据信号(RGB)输入、控制信号输入(sync与blankn)以及RGB信号DA输出行同步与场同步信号与经VGADAC产生的RGB数据信号一并输出到VGA接口,驱动CRT显示在本设计中时钟信号65MHz、同步信号为horsync与versync相与产生,有效显示区信号为行与场的有效数据区信号相与产生

一维矢量信号显示方式

在二维的空间中显示一维矢量信号,常规显示方法可以是将一维信号从左至右显示,如图2(a)所示,就如在普通的示波器上观察到的一样这样,在VGA显示时,一行扫过多个采样点,需把要显示的采样点位置计算出来,当行信号扫过时,把采样点的值赋给像素点,就完成了信号的显示而对于连续的一维信号,因为行频比场频高,图2(b)的显示方法更加合适为此,将一维信号的时间轴映射到垂直方向上,幅值映射到水平方向上,当行扫描信号扫过一行时,映射一维信号的一个采样点,即一行信号对应一个像素,当完成一行信号后接着回扫,开始扫下一行一般情况下,场频确定后,就可以根据一维信号的频率确定出一场可以显示的周期数,当完成一场信号后,在屏幕上就显示一帧图像

在具体实现时,需要对一维正弦波信号的参数作两点控制:控制正弦波的频率,保证一行扫描对应一个采样点;控制正弦波的幅度,将其控制在1024×768的有效显示区域中

对正弦波频率来说,如果频率太高,一行会扫到多个采样点;如果频率太低,一整屏无法显示一个完整周期的信号在本设计中,用一个较低的采样时钟控制正弦波的采样,正弦波存放在一个查找表中如果要在一屏中显示n个周期的正弦信号,那么需要的采样频率fs=刷新率×n×查找表中一个周期的点数

控制正弦波幅度即让正弦波的最大值不能超出屏幕的显示区VGA有效显示宽度为1024,则屏幕两端的空闲部分宽度(图2(a)和(c))都为100

(a);(b)

图2 一维正弦波VGA显示示意图

二维图像信号的显示方式

二维图像的显示过程较一维信号容易实现对二维图像,可以将二维图像信号转变成一维像素序列在屏幕显示区域内,当行与场同步信号扫过时,将该像素点对应的RGB值进行赋值,就可以完成二维图像的显示对于本设计,VGA时序为1024×768模式,图像的像素数在这个范围内可以完全在屏幕上显示,不会发生像素丢失如果图像比较小,还可以将图像控制在屏幕的任意区域内由于图像大小受存储空间限制,如果想要实现更高像素点的图像,就必须借用外部的SRAM或SDRAM来做图像缓存

Avalon MM接口控制

在DSP Builder中,Altera提供了本设计与SOPC的接口——Avalon MM接口

Avalon MM接口定义的接口信号主要有片选、读使能、写使能、地址,以及数据等根据外设的逻辑,选用不同的接口定义信号,通过这些信号Avalon主端(CPU)可以向挂在Avalon总线上的从端外设写地址与数据信号,Avalon主端外设也可以主动去获取Avalon总线上的SRAM或SDRAM中的数据不管是主传输还是从传输,都需要符合Avalon总线的读写时序才能发起一次正确的数据传输

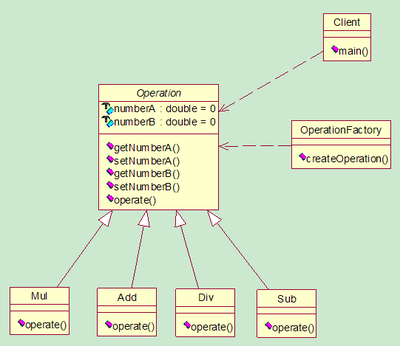

可以利用Avalon MM接口将DSP Builder中设计的模块做成自定义外设NiosⅡ CPU就可以利用Avalon总线与DSPBuilder中产生的自定义外设进行通信,在本设计中对集成到SOPC系统上的VGA接口的地址赋值为0x1后,数据写入0x1,VGA接口控制器接收到数据,就会根据设计产生VGA时序信息及RGB信号,在屏幕上显示图像图3为整个一维信号VGA显示系统的结构图

图3 系统结构图

仿真与硬件验证

本设计在2C70 DSP硬件开发平台下验证

借助于DSP Builder中的SignalComplier模块,可以容易地将设计完成的系统直接转化成RTL级的硬件描述语言,在QuartusⅡ下完成VGA时序的验证与正弦波信号的下载与显示

从显示器上硬件仿真结果来看,正弦波的幅度在有效的显示区域内呈周期性变化,因此当显示器与VGA口的J21相连时,屏幕上正弦波幅度在设计的范围内显示,一幅屏幕所显示的周期数和DSPBuilder中所设定的一致在此基础上还可以调整正弦波的采样频率,控制正弦波的显示频率与幅度大小,实现示波器的功能,观察FPGA内部的信号

结语

随着VGA接口的广泛使用,这种结合FPGA与DSP Builder的系统级设计方法已经展现优势从整个设计流程来看,系统的灵活性强,可靠性高,设计周期大大缩减,成本降低,且系统的可扩展性强未来,VGA接口的图像与视频监控系统应用将会很有市场

嵌入式系统的VGA接口设计

引言

目前越来越多的嵌入式处理器上集成了LCD控制器。典型的如三星的S3C2410A,INTEL的Xscale系列。这样可方便地外接大屏幕的LCD,且分辨率也能达到640×480,甚至800×600;色深能从6.5万色(16位)到26万色(18位)。但是大屏幕LCD的价格都比较昂贵。另一方面,普通计算机的VGA接口显示器,保有量巨大、技术成熟,如果能通过接口转换手段,让嵌入式处理器直接支持VGA显示器,则能很大地利用现有资源,节约系统成本。

LCD接口转换为VGA接口

VGA (VIDEOGraphics Array)接口信号为模拟信号。其关键信号有5个,分别是HorizONtal Sync水平同步信号(也叫行同步信号),垂直同步信号VerticalSync(也叫场同步信号),Red红色,GREEN 绿色和Blue蓝色。电子枪从左至右,从上至下地进行扫描,每行结束时,用行同步信号进行同步;扫描完所有行后用场同步信号进行场同步。因电子枪偏转需要时间,所以扫完回转中,要对电子枪进行消隐控制:在每行结束后的回转过程中进行行消隐;在每场结束后的回转过程中进行场消隐。消隐过程中不发送电子束。

扫描式LCD接口(以S3C2410A的LCD控制器为例图1),在每一场完毕后,也是用VSYNC来进行场同步;每一行完毕后,也是用HSYNC进行行同步;也有VCLK像素时钟,用于锁存数据;

其场同步信号,宽度为(VSPW+1),之前有场消隐前肩(VFPD+1),之后有场消隐后肩(VBPD+1);

其行同步信号,宽度为(HSPW+1),之前有行消隐前肩(HFPD+1),之后有场消隐后肩(HBPD+1);

可以发现,扫描式LCD接口的同步信号时序和VGA接口是一致的。原因是发明LCD后,尽管显示原理不同,但为了在时序上和CRT兼容,也采用了这样的控制时序。基于此,完全能将LCD接口转换为VGA接口。

图1 三星S3C2410A的LCD信号时序图(来自S3C2410A数据手册)

方案实现

VGA接口只需Hsync和Vsync两个同步信号和RGB三个色彩分量信号。而扫描式LCD接口的同步信号的时序和VGA接口的完全一致,可直接把两个同步信号接入VGA接口。

S3C2410A的LCD控制器输出的是RGB数字信号。因此若用一些DAC芯片把RGB数字信号转换为模拟信号,即可实现VGA接口的RGB信号输入。这类视频专用DAC芯片较多,例如ADI公司的ADV7120;CHRONTEL公司的CH7004C。实验中选用的CHRONTEL公司的CH7004C。S3C2410A的LCD控制器与CH7004C的连接如表1。

表1 S3C2410A的LCD控制器与CH7004C的连接

在选择数据格式时,RGB565较合适,因为16位数据已经有6.5万色,完全足够;24位数据时每个像素实际占用32位,4个字节,传输时对S3C2410A的总线资源占用太大。

整个电路原理图如图2所示。其中一些需要注意的地方有:

CH7004C工作在从模式下,由S3C2410A的I2C控制。在实验中使用的是精度较好的日本村田(murata)的阻容元件,包括10K,360欧,75欧和10pF的电容。10K用于I2C总线的上拉,360欧用于RSET引脚接地;75欧为R,G,B三个输出管脚和地之间的终端电阻,10pF电容用于晶振。另外,CH7004C的IIC地址,是通过把ADDR引脚拉高或拉低来设定;接地时,根据芯片手册,其7位的I2C地址为1110110,最后加一个读/写位。

图2 CH7004C的电路原理图

CH7004C的关键寄存器及设置CH7004C片内有25个寄存器。其中比较关键的是Display Mode,InputData Format,Sync Polarity三个寄存器。DisplayMode显示模式寄存器,片内地址0X00,输入分辨率为640×480,由芯片手册,可选模式从Mode13到Mode17均可。实验中选择的是默认的Mode17,对应参数为0X6A。InputDataFormat输入数据格式寄存器,片内地址是0X04,因为输入的数据格式为RGB565,且需打开pass-through模式,故对应参数为0X20。SyncPolarity同步信号极性寄存器,片内地址0X0D,根据输入的Hsync和Vsync的极性来设定,如果是均为负脉冲,则把VSP位和HSP位都置0;如果均为正脉冲,则把VSP位和HSP位都设置为1。实验中,把S3C2410A的LCD控制器的同步信号极性均设为低电平有效,故参数为0X00。

S3C2410A的LCD控制器设置

作为输出源,S3C2410A的LCD控制器也需要进行相应设置。需要的输出分辨率是640×480,16位色(RGB565格式),刷新率60Hz。一共有LCDCON1到LCDCON5共5个寄存器需要设置,具体参数要参考VGA时序规范和LCD时序图(图1)。所需设置的寄存器如表2。

表2 S3C2410A的LCD控制器中需要设置的寄存器

S3C2410A的LCD控制器设置

作为输出源,S3C2410A的LCD控制器也需要进行相应设置。需要的输出分辨率是640×480,16位色(RGB565格式),刷新率60Hz。一共有LCDCON1到LCDCON5共5个寄存器需要设置,具体参数要参考VGA时序规范和LCD时序图(图1)。所需设置的寄存器如表2。

表2 S3C2410A的LCD控制器中需要设置的寄存器

实验及数据

实验中,选择的操作系统嵌入式Linux,内核版本2.4.18,图形系统是Qtopia1.7.0。bootloader选用的韩国MIZI公司的vivi。上电后,vivi将进行初始化,其中包括设置CH7004,然后再引导进入Linux。对CH7004的操作,完全可以看作对一个IIC接口的EEPROM来进行,可专门定义一个函数IIC_Write()来写数据。例如对IDF寄存器的设置为I2C_Write(0xec,0x04,0x20)。设置好后,CH7004的所有寄存器数据如表3。

实验中还发现,设定SPR同步信号极性寄存器时,如果都设同步信号为正脉冲有效,接显示器也能正常显示,但是有闪烁。负脉冲有效则无这种情况,故推荐均设置为负脉冲有效。

表3 正常工作时,CH7004C的各个寄存器读出的数据

结语

本文提供的LCD接口转换为VGA接口的解决方案,经过实际验证,切实可行。在Linux和Windows CE4.2两种嵌入式操作系统下均进行了测试,Linux下VGA显示器的画面非常稳定;在Windows CE4.2下基本稳定,略有闪烁。该方案最大特点在于让嵌入式系统直接支持VGA显示器,具备较大的实际应用意义。

图3 Linux下外接VGA显示器

ARM嵌入式平台的VGA接口设计

大多数嵌入式产品的显示终端都选择LCD,但在某些需要大屏幕显示的应用中,工业级LCD的价格比较昂贵,且现有的大屏幕显示器(包括CRT显示器和LCD显示器)一般都采用统一的15针VGA显示接口。三星公司ARM9芯片S3C2410以其强大的功能和高性价比在目前嵌入式产品中得到广泛的应用。笔者在开发基于ARM嵌入式平台的血液流变测试仪的过程中,成功地利用高性能视频D/A转换芯片ADV7120,将S3C2410自带的LCD扫描式接口转换为VGA接口,使之能够驱动VGA接口的显示器。1 VGA接口介绍

近年来,业界制定出了众多数字化的显示接口协议,较为典型的是DVI(Digital VisualInterface)。由于数字接口的标准还未统一,厂商支持各自的标准,导致数字接口的标准迟迟未定。VGA接口是一个模拟信号接口。作为在显示领域多年的接口标准,直到今天它仍是所有显示终端最为成熟的标准接口,现在某些高端的电视也支持VGA接口。

15针VGA接口信号定义如表1所列。除了2个NC信号、3根显示数据总线和5个GND信号,比较重要的信号是3个RGB彩色分量信号和2个扫描同步信号HSYNC和VSYNC。VGA接口中彩色分量采用RS343电平标准。RS343电平标准的峰峰值电压为1V。该标准定义的4个电平范围是:

白电平--+0.714 V;

黑电平--+0.054 V;

消隐电平--0 V;

同步电平---0.286 V。

2 S3C2410 LCD控制器简介

三星公司的ARM9芯片S3C2410功能强大,性价比高,在目前的嵌入式产品中得到了广泛的应用。S3C2410带有LCD控制器,可以很方便地控制驱动扫描式接口的LCD显示。

2.1 引脚功能信息

LCD控制器提供了扫描式数据传输引脚和时序控制引脚,具体描述如下:

VFRAME/VSYNC--LCD控制器和LCD驱动器之间的帧同步信号。该信号告诉LCD屏新一帧开始了。LCD控制器在一帧显示完成后立即插入一个VFRAME信号,开始新一帧的显示。

VLINE/HSYNC--LCD控制器和LCD驱动器之间的行同步脉冲信号。该信号用于LCD驱动器将水平线(行)移位寄存器的内容传送给LCD屏显示。LCD控制器在整行数据移人LCD驱动器后,插入一个VLINE信号。

VCLK--LCD控制器和LCD驱动器之间的像素时钟信号。LCD控制在VCLK的上升沿处送出数据,LCD驱动器在VCLK的下降沿处采样。

VM/VDEN--LCD驱动器的AC信号。VM信号被LCD驱动器用于改变行和列的电压极性,从而控制像素点的显示。VM信号可以与每帧同步,也可以与可变数据的VLINE信号同步。

VD[23:0]--LCD像素数据输出端口。

2.2 寄存器

S3C2410的LCD控制寄存器主要有:LCDCON1寄存器、LCDCON2寄存器、LCDCON3寄存器、LCDCON4寄存器、LCDCON5寄存器。这些寄存器的设置与显示屏信息、控制时序和数据传输格式等密切相关,在设计中需要根据显示设备的具体信息正确设置这些寄存器才能使S3C2410正常控制驱动不同的显示屏。

2.3 内部结构

S3C2410的LCD控制器用来传输图像数据并产生相应的控制信号,由REGBANK(控制寄存器组)、LCDCD-MA(专用DMA)、VIDPCS(视频信号处理单元)、LPC3600和TIMEGEN(时序信号产生单元)组成,如图1所示。其中REGBANK包含17个可编程寄存器和几个256×16的调色板存储器,用来配置LCD控制器并设置相应的参数;而LCDCDMA提供了视频信号的快速传输通道,自动通过系统总线从系统帧缓存中取出视频数据并传输到视频信号处理单元;VIDPCS将专用DMA中取出的信号整形并提高驱动能力等处理后,输出到外部数据端口VD[23:0];TIMEGEN和LPC3600负责产生LCD所需要的控制时序。

3 VGA接口设计

利用高性能视频D/A转换芯片ADV7120将S3C24l0自带的LCD扫描式接口转换为VGA接口,然后用带有VGA接口的显示器显示。

3.1 ADV7120简介

ADV7120是美国ADI公司生产的高速视频数模转换芯片,其像素扫描时钟频率有30 MHz、50 MHz、80MHz三个等级。ADV7120在单芯片上集成了3个独立的8位高速D/A转换器,可以分别处理红、绿、蓝视频数据,特别适用于高分辨率模拟接口的显示终端和要求高速D/A转换的应用系统。

ADV7120的输入及控制信号非常简单:3组8位的数字视频数据输入端,分别对应RGB视频数据,数据输入端采用标准TTL电平接口;4条视频控制信号线包括复合同步信号SYNC、消隐信号BLANK、白电平参考信号REFWHITE和像素时钟信号CLOCK;外接一个1.23V数模转换参考电压源和1个输出满度调节。只有4条输出信号线:模拟RGB信号采用高阻电流源输出方式,可以直接驱动75Ω同轴传输线;同步参考电流输出信号Isync用来在绿视频模拟信号中编码视频同步信息。

3.2 原理图设计

VGA接口的同步信号和LCD扫描式接口的同步信号是一致的。利用ADV7120可以方便地将S3C24l0的LCD扫描式接口转换成VGA接口,电路原理如图2所示。

S3C2410处理器接口中的同步扫描信号HSYNC和VSYNC直接接到VGA接口,VDEN信号(显示数据有效信号)则被用于控制ADV7120芯片。由于ADV7120对参考电平的要求精度很高,不能以电阻分压电路代替。在此采用了1.2V电压基准芯片AD589来产生参考电压。该电路设计中需要注意的是【】,在PCB布板时要将模拟地和数字地分开。

4 S3C2410相关寄存器设置

以分辨率为640×480、刷新频率为60Hz、16位彩色显示模式为例,根据图3所示VGA接口同步信号时序,介绍S3C2410中LCDCON1~LCDCON5寄存器的设置。

4.1 LCDCONl寄存器

LINECNT:行计数器的状态位。只读,不用设置。

CLKVAL:确定VCLK频率的参数。公式为VCLK=HCLK/[(CLKVAL+1)×2],单位为Hz。笔者所用的硬件系统HCLK=100MHz,640×480的显示屏需要VCLK=20 MHz,故需设置CLKVAL=1。

MMODE:确定VM的改变速度。在此选择MMODE=O,为每帧变化模式。

PNRMODE:确定扫描方式。选择PNRMODE=0x3,为TFT LCD面板扫描模式。

BPPMODE:确定BPP(每像素位数)模式。在此选择BPPMODE=0xC,为TFT 16位模式。

ENVID:数据输出和逻辑信号使能控制位。选择ENVID=1,为允许数据输出和逻辑控制。

4.2 LCDCON2寄存器

VBPD:确定帧同步信号和帧数据传输前的一段延迟时间,是帧数据传输前延迟时间和行同步时钟间隔宽度的比值,如图3,VBPD=t3/t6=1.02mS/31.77μs=32。

LINEVAL:确定显示的垂直方向尺寸。公式:LINEVAL=YSIZE-1=479。

VFPD:确定帧数据传输完成后到下一帧同步信号到来的一段延迟时间,是帧数据传输后延迟时间和行同步时钟间隔宽度的比值,如图3,VFPD=t5/t6=0.35ms/31.77μs=11。

VSPW:确定帧同步时钟脉冲宽度,是帧同步信号时钟宽度和行同步时钟间隔宽度的比值。如图3,VSPW=t2/t6=0.06ms/31.77μs=2。

4.3 LCDCON3寄存器

HBPD:确定行同步信号和行数据传输前的一段延迟时间,描述行数据传输前延迟时间内VCLK脉冲个数,如图3,VBPD=t7×VCLK=1.89μs×25MHz=47。

HOZAL:确定显示的水平方向尺寸。公式HOZAL=XSIZE-1=639。

HFPD:确定行数据传输完成后到下一行同步信号到来的一段延迟时间,描述行数据传输后延迟时间内VCLK脉冲个数,如图3,HFPD=t9×VCLK=0.94μs×25 MHz=24。

4.4 LCDCON4寄存器

HSPW:确定行同步时钟脉冲宽度。描述行同步脉冲宽度时间内VCLK脉冲个数,如图3,HSPW=3.77μs×25MHz=94。

4.5 LCDCON5寄存器

VSTATUS:垂直方向状态。只读,不用设置。

HSTATUS:水平方向状态。只读,不用设置。

BPP24BL:确定显示数据存储格式。此处设置BPP24BL=0x0,为小端模式存放。

FRM565:确定16位数据输出格式。此处设置FRM565=0x1,为5:6:5格式输出。

INVVCLK:确定VCLK脉冲有效边沿极性。根据屏幕信息确定,此处选择INVVCLK=0xl,VCLK上升沿到来时数据传输开始。

INVVLlNE:确定HSYNC脉冲的极性。由图3可知,为负极性,设置INVVLINE=0x1选择负极性脉冲。

INVVFRAME:确定VSYNC脉冲的极性。由图3可以看出,为负极性,故设置INVVFRAME=0x1选择负极性脉冲。

INVVD:确定数据输出的脉冲极性。根据屏幕信息确定,此处设置INVVD=0x0选择正极性脉冲。

INVVDEN:确定VDEN信号极性。根据屏幕信息确定,此处设置INVVDEN=0x0为正极性脉冲。

INVPWREN:确定PWREN信号极性。根据屏幕信息确定,此处设置NVPWREN=0x0为正极性脉冲。

INVLEND:确定LEND信号极性。根据屏幕信息确定,此处设置INVLEND=0x0为正极性脉冲。

PWREN:PWREN信号输出允许。设置PWREN=0xl,允许PWREN输出。

ENLEND:LEND输出信号允许。设置ENLEND=0x1,允许LEND输出。

BSWP:字节交换控制位。根据各自需要设置,此处设置BSWP=0x0,禁止字节交换。

HWSWP:半字交换控制位。根据各自需要设置,此处设置HWSWP=0xl,使能半字节交换。

5 讨论与总结

S3C2410处理器能够驱动24位颜色模式的VGA接口,但当处理器数据总线负载过大时,显示效果就不太理想。具体分析所需数据带宽如下:

S3C2410处理器工作在640×480×60 Hz×24位(分辨率为640×480、刷新频率为60Hz、24位色彩)模式下的数据带宽为:640×480×60×4/(1 024×1024)=70.3MB/s(24位颜色实际占用32位数据量),这些数据都需要利用DMA方式通过系统的数据总线从SDRAM中获得。而S3C2410处理器在100MHz的总线频率下,32位内存的峰值带宽是100×32/8=400MB/s,实际带宽也就100~200 MB/s。那么70.3MB/s的显示数据对于S3C2410处理器过于沉重了,显示器的屏幕经常会出现短暂的黑屏。这是因为系统总线太忙,LCD扫描式接口的数据跟不上,扫描时钟的频率暂时变慢导致CRT显示器的同步信号不符合规范所致。若用16位颜色模式,则数据带宽减为640×480×60×2/(1024×1 024)=35.2MB/s。实际测试中,工作在16位颜色模式下,可以正常显示60Hz下的640×480的VGA图形。

综上分析,如果要支持高分辨率和高刷新率的显示,需要比较大的数据带宽,对处理器的频率和总线频率要求较高。目前的嵌入式处理器在这些方面有很大的限制,不过本设计可以完全支持16位色彩下640×480×60Hz显示模式的CRT显示,并且如果采用LCD作为显示界面,LCD对刷新率的要求和CRT显示器不同,LCD可以在刷新率为30Hz的情况下正常显示。本设计对解决基于ARM的嵌入式系统中大屏幕显示方面的问题有很大的实用价值和借鉴意义。

爱华网

爱华网