逻辑分析的概念

逻辑分析仪也是非常常用的仪表,与示波器一样,是数字设计和测量的经典仪器之一。数字电路测量时,何时应使用示波器呢?一般而言,当需要精确参数信息(如时间间隔和电压读数)时可以使用示波器。具体来讲:

图1 示波器用于测量信号的模拟波形

一般而言,逻辑分析仪用于查看多个信号之间的定时关系,或者用于捕获信号所运载的数据。当被测设备的信号超过电压阀值时,逻辑分析仪会表现出与逻辑电路相同的反应。它将识别信号的高低。具体来讲:

上面已经简短讨论了逻辑分析仪的一些用法,现在,让我们更详细地了解一下有关逻辑分析仪的概念。到目前为止,我们已经很广泛地使用了“逻辑分析仪”这一术语。实际上,大多数逻辑分析仪中都包含两个分析仪。

1.定时分析仪:

定时分析仪是逻辑分析仪的一部分,它与示波器相似。事实上,它们之间的关系非常密切。定时分析仪显示信息的一般形式,这一点与示波器相同,即横轴表示时间,纵轴表示电压振幅。因为两个仪器上的波形都取决于时间,所以这种显示可以说是“时间域”中的显示。

2.状态分析仪:

状态分析仪非常适用于跟踪软件中的缺陷或硬件中的缺陷组件。它有助于确定问题是出现在软件代码中还是出现在某些硬件设备中。大多数情况下,状态分析仪用于在出现特定时钟信号时查找总线上存在哪些逻辑电平。换句话说,可以了解在时钟出现且假设数据有效时将显示哪些“活动状态”。内存中采集的数据将以列表格式显示,且带有连接到各个状态的时间标签。

定时分析

定时分析仪使用自己的内部时钟控制数据采样。这种类型的时钟计时会使逻辑分析仪中的数据采样与被测设备中的时钟异步。具体来讲:

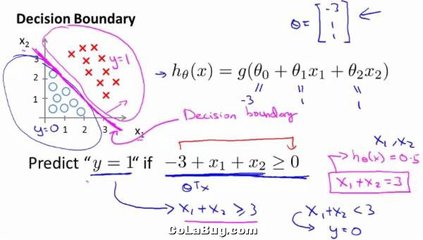

在定时采集模式下,逻辑分析仪的工作是对输入波形进行采样,从而确定它们是高电平还是低电平。为了确定高低,逻辑分析仪会将输入信号的电压电平与用户定义的电压阈值进行比较。如果采样时信号高于阈值,则分析仪将信号显示为1 或高。同样,低于阈值的信号将显示为 0 或低。下图阐释了当正弦波跨过阈值电平时逻辑分析仪对其进行采样的情况。

图2 定时分析采集原理

采集之后采样点被存储在内存中,并用于重建方形数字波形。这种要使一切变成方形的处理方式似乎会限制定时分析仪的用处。不过定时分析仪本来也不是打算用作参数仪器的。若要查看信号的上升时间,可以使用示波器。若需校验几个或几百个信号之间的时序关系,对其同时进行查看,则定时分析仪才是正确的选择。

定时分析仪对输入通道进行采样时,该通道信号或者是高电平或者是低电平。如果在进行某一采样时该通道处于某种状态(高或低),而在进行下一采样时变成了相反的状态,则分析仪可以“知道”输入信号已在这两个采样之间的某个时候发生了跳变。但它不知道具体在何时,因此它将跳变点放在了后一个采样上,如下图所示。

图3 定时分析采样精度(不确定度)

对于跳变实际上是在何时发生以及分析仪何时显示跳变,存在着某种含糊性。假如跳变是在前一个采样点之后立即发生的,这种不确定性最多也就是一个采样周期。不过对于这种方法,在精度和总采样时间之间也存在着一种折衷。请记住,每个采样点都只使用一个存储位置。因此,精度越高(采样频率越高),采样周期越短。

触发定时分析仪:

在测量中的某些点,逻辑分析仪必须了解何时采集(存储)流经其内存的数据。这些点叫做触发点。

使分析仪触发的一种方法是:相应地配置分析仪,使之从一组信号(总线)中查找上限或下限码型,或者查找单个信号的上升或下降时钟沿。当分析仪在数据中发现指定的码型或时钟沿时,它便触发。

码型触发:

码型触发用于在总线上查找特定的上限和下限码型。您可以指定不同的标准,如等于、不等于、在或不在某个范围内或者大于/小于。

示例:拥有一条包含 8 条信号线的总线。配置了简单触发 以指定分析仪在输入数据等于“AA”码型时触发。 |

图4 码型触发

为了更便于某些用户的使用,大多数分析仪上的触发点不仅可以用十六进制进行设置,还可以用二进制(1 和 0)、八进制、ASCII或十进制进行设置。例如,十六进制触发值 AA 还可以设置为等价的二进制触发值 1010 1010。但是,在 16、24、32 或 64位宽的总线上查找时,使用十六进制设置触发点尤其有帮助。

时钟沿触发:

时钟沿触发对于习惯使用示波器的用户来说是一个很熟悉的概念。调整示波器上的“triggerlevel”(触发电平)旋钮时,可以将其视为设置电压比较仪的电平:当输入电压超过该电平时,电压比较仪会告知示波器触发。定时分析仪的时钟沿触发大体上与此相同,只不过将触发电平预先设置成了一个逻辑阈值。

许多逻辑设备依赖于电平,而这些设备的时钟和控制信号却往往受时钟沿的影响。通过时钟沿触发,可以在对设备进行定时的同时开始采集数据。

示例:试想一个未正确移位数据的时钟沿触发移位寄存器。是数据有问题还是时钟沿有问题?为检测设备,我们需要在对其进行定时的同时检验数据(基于时钟沿)。可以告知分析仪在出现时钟沿时(无论上升或下降)采集数据并获取移位寄存器的所有输出。 |

图5 边沿触发

跳变定时:

在Transitional / Storequalified(跳变/存储限定)定时模式中,定时分析仪将定期对数据进行采样,但只有当阈电压电平中存在信号转变时才存储数据。每当定义的总线/信号(未排除的)中的任何位发生转变时,都要存储所有通道上的数据。为每个存储数据样本存储一个时间标签,这样稍后就可以重新构建和显示测量。

通常,各个采样点不会发生转变。下面将用时间标签2、5、7 和 14 来举例说明。当确实发生转变时,为每个转变存储两个样本。因此,存储 1K 的转变,就会带有 2K内存的样本。必须去除一个起始点必需的转变才能使存储的最小转变量达到 1023。

如果转变发生的速率很快,例如每个采样点都有一个转变,那么如下图中的时间标签17 至 21 所示,只为每个转变存储一个样本。如果整个跟踪过程始终保持这种状况,那么存储的转变数量为 2K样本。此外,必须去除起始点样本,这样才能使存储的最大跳变量不超过 2047。

图6 跳变定时的数据存储

大多数情况下,当最小转变量和最大转变量都存在时会存储跳变时序跟踪。因此,在此例中存储的实际转变量将在1023 和 2047 之间。

跳变定时注意事项:

检测到时钟沿时,在分配给定时分析仪的所有通道中存储两个样本。如果在时钟沿检测器重置之前出现第二个时钟沿(在第一个时钟沿后),为避免数据丢失需要两个样本。

在跳变定时中,每个序列步骤只有 2 个分支。在跳变时序中,只有一个全局计数器可用。

跳变时序需要有时间标签才能重建数据。通过将时间标签与内存中的测量数据交叉可存储时间标签。

默认情况下,分析仪将查找为逻辑分析仪模块定义的所有总线/信号上的转变。但是,为增加可用内存深度和采集时间,可以在高级触发中选择不存储某些总线/信号转变(如将无用信息添加到测量中的时钟或选通脉冲信号)。

运行测量时,无论总线/信号是否定义或是否分配给逻辑分析仪通道,都将在所有这些通道上采集数据。在跳变时序模式中,如果定义的总线/信号(未排除的)上存在转变,将保存采集的样本。

运行跳变时序测量后,如果为以前未分配的逻辑分析仪通道定义新的总线/信号,那么将显示在这些通道上采集的数据,但是不可能存储这些总线/信号上的所有转变;显示的数据好似新的总线/信号在运行测量前就已经被排除了。

在跳变时序中,不需要预先存储数据(触发前获得的样本)。因此,与状态模式非常相似的是,触发位置(起始/中心/结束)表明触发后样本占用内存的百分比。触发前获得/显示的样本数量在不同的测量中会有所变化。

状态分析

状态分析仪需要来自被测设备的采样时钟信号。这种类型的时钟计时可使逻辑分析仪中的数据采样与被测设备中的计时事件同步。具体来讲:

对于微处理器,数据和地址可以出现在相同的信号线上。要采集正确的数据,逻辑分析仪必须对数据采样加以限制,使之只在所需的数据有效并出现在信号线上时进行。为此,它会从相同的信号线上采集数据样本,但使用来自被测设备的不同采样时钟。

示例:以下时序图表明,要采集地址,分析仪需要在 MREQ 线下降时进行采样。 |

图7 状态采集

触发状态分析仪:

与定时分析仪相似,状态分析仪也具有限定要存储的数据的功能。如果我们正在查找地址总线的上限和下限的特定码型,当分析仪找到该码型时,我们可以通知分析仪开始存储,并且只要分析仪的内存未满就一直存储。

简单触发示例:

请看下面显示的“D”触发器,在正值的时钟沿出现之前,“D”输入上的数据是无效的。因此,时钟输入为上限时,触发器的状态才有效。

图8 D触发器

现在,假设我们有并行的八个此类触发器。如下所示,这八个触发器都连接到同一时钟信号。

图9 接收器

当时钟线上出现高电平时,所有这八个触发器都会在其“D”输入处采集数据。此外,每次时钟线上出现正电平时都会发生有效状态。下面的简单触发指示分析仪在时钟线上出现高电平时在D0 - D7 这几条上收集数据。

图10 总线收集的数据

高级触发示例:

假设想查看地址值为406F6 时内存中存储了哪些数据。对高级触发进行配置,以在地址总线上查找码型 406F6(十六进制)以及在RD(内存读取)时钟线上查找高电平。

图11 高级触发设置

在配置 EdgeAnd Pattern trigger(时钟沿和码型触发)对话框时,尝试将该操作看作是构造从左向右读取的句子。

Find the first occurrence of a Bus named ADDR, andon All bits a pattern that Equals 406F6 Hex,And a Signal named RD with a High level.ThenTrigger and fill memory with Anything.

Pod、通道和时间标签存储

Pod和通道的命名约定:

Pod是一组逻辑分析仪通道的组合,共有17个通道,其中数据16个通道,时钟1个通道。逻辑分析仪的通道数是Pod数的倍数关系。34通道的逻辑分析仪对应两个Pod,68通道逻辑分析仪对应4个Pod,136通道逻辑分析仪对应8个Pod。

对于模块化的逻辑分析仪(或称为逻辑分析系统),以16900系列逻辑分析系统为例,对应关系如下:

在 16900系列逻辑分析系统中,请勿混淆时钟通道 C2 与 Slot C 中的 Pod 2,后者记作 Pod C2。对于时钟通道,C 是Clock 的缩写,不是 Slot C 的缩写。

为什么有时Pod会丢失?

导致所有Pod对逻辑分析仪模块均不可用的原因有多种:

该模块是已分离的逻辑分析仪的一部分。在这种情况下,Pod位于分离分析仪的另一半模块中。

状态模式和跳变定时模式下通道数、内存深度和触发之间的相互影响:

状态采样模式时,时间标签存储需要1个Pod或1/2的采集内存。

默认设置:

跳变定时模式,时间标签存储需要1个Pod或1/2的采集内存:

状态模式采样位置、眼定位和眼图扫描

同步采样(状态模式)逻辑分析仪与触发时钟沿的触发相似,因为它们都需要输入逻辑信号才可以在时钟事件前(建立时间)和时钟事件后(保持时间)的一段时间内保持稳定,以便正确解释逻辑电平。组合建立和保持时间被称为建立/保持窗口。

被测设备(由于其本身的建立/保持要求)可指定数据在某段时间内在总线上有效。这被称为数据有效窗口。一般情况下,大多总线上的数据有效窗口小于总线时间周期的一半。

要精确采集总线上的数据,需符合以下条件:

图13 调整采样位置

为了将建立/保持窗口(采样位置)放置在数据有效窗口内,逻辑分析仪可在每次采样输入时调整延迟(以定位每个通道的建立/保持窗口)。

如果可以在单个通道上调整采样位置,可以使逻辑分析仪的建立/保持窗口变小,因为可以校准由探头电缆和逻辑分析仪的内部电路板跟踪引起的偏移效应,而且还可以看到逻辑分析仪的内部采样电路的建立/保持要求。

但是,手动定位每个通道的建立/保持窗口需要花费大量时间。对于被测设备中的每个信号和每个逻辑分析仪通道来说,必须测量与总线时钟(带有示波器)相关的数据有效窗口,重复定位建立/保持窗口并运行测量以查看逻辑分析仪是否正确采集数据,最后再将建立/保持窗口定位在错误采集数据的位置之间。

使用具有眼定位 (eyefinder)功能的逻辑分析仪,在手动调整(没有额外的被测设备)的一小段时间内,可以自动:

眼定位 是获得尽可能小的逻辑分析仪建立/保持窗口的一种简单方法。

眼定位概要:

对于指定的状态采样时钟,眼定位可在时钟沿前后的一个固定时间范围内查找数据信号转变(阈电压交叉点),并为显示相关内容以帮助设置最佳采样位置。

为了了解眼定位显示,需为每个活动时钟沿拍摄一张有关该时钟沿的数据信号转变的“照片”。将此照片看作快照、定格画面或频闪观测仪(位于时钟沿中心或与时钟沿同步)。到达时钟沿的时间为T=0。

例如,如果选择盒1 上时钟输入的上升沿作为状态采样时钟,每次拍摄“照片”时,都将达到盒 1 时钟上的上升沿。盒 1时钟沿之间的时间是否相同无关紧要。如果同时在上升沿和下降沿上进行采样,那么在每一个时钟沿上都会拍摄一张“照片”。此外,在活动沿之间消耗了多少时间也不重要。每一个时钟沿上都要拍摄“照片”。

要构建眼定位 显示,需要将无数张这样的“照片”堆叠在彼此的顶端。每张“照片”都在 T=0时对齐,此时将达到活动时钟沿。照片拍自上升沿还是下降沿并没有关系;它们会在 T=0时对齐。构建显示后,就无法区分给定信号转变区域是与时钟上升沿相关联,还是与下降沿(或两者)相关联。

眼定位工作原理:

通过逻辑分析仪使用少量的偏移延迟对每个通道进行双重采样的功能,以及通过使用独有的 OR操作比较延迟的样本可进行眼定位 测量。

图14 眼定位 工作原理

当独有的 OR输出很高时,延迟的样本会有所差别,并且会在延迟时间之间检测到转变。

由于采样信号的不稳定和其他变化,眼定位测量将对每对延迟值的多个时钟进行检查,以便报告两次延迟时间之间发生转变的频率。

然后,检查另一对延迟值,依次类推,直到扫描完转变的整个时间范围。

图15 延迟值记录

因为逻辑分析仪可以调整通道的阈电压,所以眼定位 测量可在很多阈电压电平随着时间的推移对转变进行重复扫描。

图16 眼定位的多阈值扫描

通过调整阈电压和查看活动指示符,眼定位可查找信号活动信封并确定最佳阈电压;然后通过在该阈值执行全时扫描,眼定位 可找出样本位置。

图17 眼定位的阈值和采样位置扫描

也可以在当前阈电压设置下运行全时扫描,以便仅自动设置采样位置。

图18 仅扫描采样位置

自动阈值和采样位置设置扫描通常足以确保正确采集数据,但它还可以识别您想要进一步详细查看的信号(例如,如果您想查看延迟、衰减等)。通过在整个信号活动信封内执行全时扫描,眼定位可以显示在时间和电压的小窗口中检测到的转变。这些扫描称为眼图扫描(eyescan)。像示波器一样,眼图扫描用于显示测量数据。每个窗口中的转变数量都会突出显示。这可以使概览眼型图案,并确定是否需要使用示波器来进一步详细地查看信号。

图19 眼图扫描

可以运行导致自动设置阈电压和采样位置的 eye scan,或运行只导致自动设置采样位置的 eyescan。

眼定位测量收集数据所基于的通道数量会影响测量时间。当一个模块中存在多个逻辑分析仪卡时将出现异常;在这种情况下,测量将同时并行运行。

支持差分信号的逻辑分析仪中的眼图扫描Eye Scan:

支持差分信号的逻辑分析仪(如16962A 逻辑分析仪模块)针对输入使用真值差分接收器:

可编程参考电压将计入负输入。这是分析仪采用单端探头时的阈电压。对于差分探测的相关操作,通常将参考电压编写为 0V:

随后将接收器的输出与0V 进行比较,从差分输入信号产生内部逻辑信号。请注意,最终比较结果将对“差分信号高于 Vref 还是低于Vref?”的问题作出解答:

对眼隙的 eye scan测量是通过使用不同 Vref 设置进行一系列 eye finder 测量完成的。差分信号的默认 eyefinder 测量使用 Vref=0V。通过将 Vref 增至零以上,我们会找到信号与上升的 Vref 值交叉的位置。如果Vref 升至足够高,信号的顶部轨迹将通过 Vref,我们便会看到眼的顶端。再将 Vref 升高一点会导致 Vcomp 保持在Vlo,表示信号不会升至该电平。反之,将 Vref 移至零以下会看到眼的下半部。

eyescan/eye finder 显示窗口会在每个信号的 eye scan 图下方显示eye finder 交叠部分,以此显示 eye finder 与 eyescan 之间的这一关系。通过在 eye scan 图中将 Vth水平线向上和向下移动,可以获得距离眼中心该偏移量位置处的 eye finder 视图。

无论用户界面中的阈值如何设置,逻辑分析仪的差分输入将始终应用于接收器。这意味着可通过将电压阈值手动设置为非零值允许在差分对中使用公共模式电压。如果信号摆幅中心与地线差距大于 100mV,eye scan 将自动执行此操作。

逻辑分析仪的触发

设置逻辑分析仪触发非常困难,而且还需花费大量时间。假设如果知道如何编程,则应该可以毫不费力地设置逻辑分析仪触发。然而,这是不可能的,因为许多概念对逻辑分析来说都是唯一的。本节的目的就是介绍这些主要概念及如何有效地使用它们。

传送带类比:我们可以将逻辑分析仪的内存比作一条很长的传送带,而从被测设备 (DUT)获取的样本就像是传送带上的箱子。新的箱子被放置在传送带一端,而在另一端落下。换句话说,由于逻辑分析仪内存的深度(样本数量)有限,因此每当采集新样本时,如果内存已满,将会删除内存中现有的最旧的样本。如下图所示。

图20 逻辑分析仪触发的传送带类比

逻辑分析仪触发就像是放置在传送带(上面放置有多个箱子)起始位置上的箱子一样。它们的任务是“查找特殊的箱子,并在该箱子到达传送带的某一特定位置时停止运行传送带”。在此类比中,特殊的箱子就是触发。逻辑分析仪检测到与触发条件相匹配的样本后,就表示当触发位于内存中的适当位置时应停止继续采集样本。

触发在内存中的位置被称为触发位置。通常,触发位置被设置在中间,以便使触发前后出现的样本的最大数量不超出内存范围。不过,也可以将触发位置设置在内存中的任意位置。

由于逻辑分析仪触发提供了大量功能,因此下表将对本文中介绍的功能进行简要概述。该表将对这些功能进行逐一描述。

表1 逻辑分析仪触发功能摘要

触发序列:

虽然逻辑分析仪触发通常很简单,但它们却需要复杂的程序。例如,可能想在某一信号的上升沿后跟另一信号的上升沿时触发。这意味着逻辑分析器必须在开始寻找下一个上升沿之前找到第一个上升沿。由于拥有一个可查找触发的步骤序列,因此它被称为触发序列。序列的每个步骤被称为一个序列步骤。

每个序列步骤由两部分组成:条件和操作。条件是指布尔逻辑表达式,例如“If ADDR = 1000”或“If there is arising edge onSIG1”。操作是指符合条件时逻辑分析仪应当执行的内容。操作的示例包括触发逻辑分析仪、转至另一序列步骤以及启动定时器。这类似于编程中的If/Then 语句。

触发序列中的每个步骤都被指定一个数字。执行的第一个序列步骤总是序列步骤1,但由于“转到”操作,剩余的序列步骤可以以任意顺序执行。

执行一个序列步骤且布尔逻辑表达式均为假时,逻辑分析仪将采集下一样本并再次执行同一序列步骤。例如一个简单的示例,考虑以下触发序列:

1. If DATA = 7000 then Trigger

如果采集以下样本,逻辑分析仪将在采集样本 #6 时触发。

样本号 ADDR DATA 1 1000 2000 2 1010 3000 3 1020 4000 4 1030 5000 5 1040 6000 6 1050 7000 <- 此处为逻辑分析仪的触发位置 7 1060 2000

实际上,序列步骤1 相当于“Keep acquiring more samples until DATA=7000, thentrigger”。

如果符合一个序列步骤中的布尔逻辑表达式,那么在执行下一序列步骤之前总是采集另一样本。换句话说,如果一个样本符合序列步骤 1的条件,在执行序列步骤 2前将采集另一样本。这意味着一个单独的样本不可能符合多个序列步骤的条件。每个序列步骤都可以看作是代表了在不同点及时发生的事件。两个序列步骤可以从不用于指定同时发生的两个事件。

例如,考虑以下触发序列:

1. If ADDR = 1000 then Go to 2 2. If DATA = 2000 then Trigger

如果采集以下样本,逻辑分析仪将在采集样本 #7 时触发。

样本号 ADDR DATA 1 1000 2000 <- 此样本符合序列步骤 #1 中的条件 2 1010 3000 3 1020 4000 4 1030 5000 5 1040 6000 6 1050 7000 7 1060 2000 <- 此处为逻辑分析仪的触发位置

请注意,由于在符合序列步骤 1 中的条件和测试序列步骤 2 中的条件二者之间采集了新的样本,因此逻辑分析仪不会在采集样本 #1时触发。可将此触发序列看作是“Find ADDR = 1000 followed by DATA = 2000 and thentrigger”。触发序列中的多序列步骤暗示了“后接”。

逻辑分析仪触发后,将不会再次触发。换句话说,即使度个样本符合触发条件,逻辑分析仪也只触发一次。例如,使用“ADDR=1000”作为触发,如果逻辑分析器采集以下样本,它将会在采集样本#2 时触发,并且只在采集样本 #2 时触发。

样本号 ADDR 1 0000 2 1000 <- 此处为逻辑分析仪的触发位置 3 2000 4 1000 <- 逻辑分析仪不会在此处再次触发 5 1040

一个经常遇到的问题是“如果不符合序列步骤中的条件会怎样?”例如,有一个条件是“If ADDR = 1000 ThenTrigger”,那么如果当前样本是 ADDR =2000,结果会怎样?逻辑分析仪只采集下一样本并试图再次执行此序列步骤。实际上,如果触发条件是“ADDR =1000”,这相当于“持续采集样本直到找到条件为 ADDR=1000的样本”。因此,如果设置一个从不符合的触发条件,逻辑分析器将不会触发。

当符合序列步骤中的条件时,使用“转到”操作时下一步将执行哪个序列步骤将会非常清楚,但是如果没有使用“转到”操作,则不可能知道执行哪个序列步骤。在一些逻辑分析仪上,如果没有“转到”,这意味着应当执行下一序列步骤。在其他逻辑分析仪上,意味着将再次执行同一序列步骤。由于比较混乱,最好使用“转到”操作而不依靠默认。状态和定时模块通过在每个序列步骤中自动包含一个“转到”或“触发”操作来解决这一问题。例如:

If ADDR = 1000 and DATA = 2000 then Go to 1 <- 这是自动添加的

布尔逻辑表达式:当多个序列步骤表示“后跟”时,可以在序列步骤内使用布尔逻辑表达式。示例:

If ADDR = 1000 and DATA = 2000 此表达式意指在同一样本中 ADDR 必须等于 1000 且 DATA 等于 2000,才能符合此表达式。换句话说,在 ADDR 等于 1000 的同时 DATA 等于 2000。因此,如果要在同时发生两个事件时触发,则应使用布尔逻辑表达式。常见错误是应使用布尔逻辑表达式时尝试使用两个序列步骤,或者应使用两个序列步骤时尝试使用布尔逻辑表达式。当多个事件同时发生时使用布尔逻辑表达式,而在一个事件接着一个事件发生时使用多个序列步骤。

分支:分支类似于C 编程语言中的 Switch 语句和 Basic 中的 Select Case语句。分支可提供测试多个条件的方法。每个分支都有其独有的操作。下面是多分支的一个示例:

1. If ADDR < 1000 then Go To 2 <- This is a branch of Level 1 Else If ADDR > 2000 then Go To 3 <- This is a 2nd branch of Level 1 Else If DATA = 2000 then Trigger <- This is a 3rd branch of Level 1 2. If DATA <= 7000 then Trigger 3. If there is a Rising Edge on SIG1, then Trigger 在序列步骤 1 中,存在三个分支,因此存在三个可以采用的操作。

如果符合某一分支的条件,则不对其下面的任何分支进行测试。换句话说,无法根据单个样本执行多个分支,即使该样本可导致符合多个分支条件。也就是说,每个分支都是一个“ElseIf”。

沿:沿表示单个信号从下到上或从上到下的转变。通常,沿被指定为“上升沿”、“下降沿”或“任一时钟沿”,其中“上升沿”表示从下到上的转变。在大多数逻辑分析仪上,触发序列中最多可包含两个沿,而有些则只允许包含一个沿。

范围:指定值的范围是划分范围的一种便捷方式,如“1000 到 2000 范围内的 ADDR”。大多数逻辑分析仪还支持“not inrange”功能。范围是一种方便的快捷方式,因此您无需指定“ADDR >= 1000 and ADDR<= 2000”。

标志:标志是用于从一个模块向另一个模块发送信号的布尔变量。当某种情况在某一模块中发生而稍后被另一模块测试时可以设置标志。在下面的示例中,标志1 用于跟踪在模块 1 的触发序列中发生的情况,以便在模块 2 中使用此信息。

模块 1的触发序列:

1. If ADDR < 5000 then Set Flag 1 Trigger and fill memory

模块 2 的触发序列:

1. If DATA = 5000 and Flag 1 is set then Trigger Else if DATA = 1000 and not Flag 1 then Trigger

计数器:发生计数器用于想要查找事件的“第 N 次”出现的情况。例如,如果想在 ADDR = 1000 第 5次出现时触发,可以将触发设置为:

If ADDR = 1000 occurs 5 times then Trigger

全局计数器类似于整数变量。全局计数器比发生计数器更灵活,因为它们可用于为复杂事件(例如一个时钟沿后跟另一时钟沿的事件)计数。可以增加、测试和重新设置全局计数器。默认情况下,全局计数器以零开头并且不需要重新设置,除非已在触发序列中使用了它们。一般情况下,如果可能的话,应使用发生计数器代替全局计数器,原因是发生计数器的用法比较简单,而且全局计数器的数量有限。

定时器:定时器用于检查事件之间消耗的时间。例如,如果想在出现一个时钟沿后的 500 ns内出现另一个时钟沿的情况下引发触发,请使用定时器。使用定时器时要记住的最关键一点是:先启动定时器,然后再对其进行测试。换句话说,定时器无法自动启动。设置定时器的关键是确定在何种情况下进行启动和测试。

存储限定:存储限定用于确定应该存储(即,存入内存)还是丢弃已获得的样本。这可以避免不需要的样本占用逻辑分析仪内存。

设置存储限定最简单的方法是设置“默认存储”。默认存储表示“如果未经序列步骤指定,则进行存储”。例如,可能只想在 ADDR 的范围为1000 到 2000 时存储样本,那么就应将“默认存储”设置为:

ADDR In Range 1000 to 2000

默认情况下,“默认存储”设置为存储所有已获得的样本。也可以将“默认存储”设置为不存储任何样本,这意味着除非某序列步骤覆盖该默认存储,否则将不存储任何样本。

序列步骤存储限定意味着在某个特定的序列步骤内只存储特定的样本。这意味着在使用Go To(转到)或Trigger(触发)操作离开此序列步骤之前,应用该存储限定。如果要为每个序列步骤应用不同的存储限定,该存储限定很有用。例如,可能不希望在ADDR = 1000 之前存储任何样本,而对于其余的测量,只存储 ADDR 在 1000 到 2000 范围之内的样本。

设置序列步骤存储还需要再使用一条分支指令。例如,在查找 DATA=005E 时,如果只希望存储 ADDR 在 5000 到 6FFF范围之内的样本,某些情况下可使用以下序列步骤:

1. If DATA = 005E then Trigger Else If ADDR in range 5000 to 6FFF then Store Sample Go to 1 注意存储样本操作的使用。这表示“立即存储内存中最新获得的样本”。而不 表示“从现在起,开始存储”。应当注意,因为当 ADDR 不在 5000 到 6FFF 范围之内时从不执行存储样本操作,所以该分支指令实质上是指“在此序列步骤中,只存储 ADDR 在 5000 到 6FFF 范围之内的样本”。

上述示例似乎说明将只存储 ADDR 在 5000 到 6FFF范围之内的样本。但是,这取决于默认存储的设置方式。还是使用上述示例,如果默认存储设置为“StoreEverything”(存储所有样本)并且有一个样本不在 5000 到 6FFF 的范围之内,则不会执行 Else If分支指令,而应用该“默认存储”。实际上,该序列步骤说明了样本值在特定范围内时要执行的操作,但没有说明样本值在此范围之外时应执行的操作。因此,如果要明确指定序列步骤存储,请使用以下指令:

1. If DATA = 005E then Trigger Else If ADDR in range 5000 to 6FFF then Store Sample Go to 1 Else If ADDR not in range 5000 to 6FFF then Don't Store Sample Go to 1 此外,如果默认存储设置为“Store Everything”(存储所有样本),可以使用以下指令:

1. If DATA = 005E then Trigger Else If ADDR not in range 5000 to 6FFF then Don't Store Sample Go to 1

总之,序列步骤存储总会覆盖默认存储,但只针对序列步骤存储中特别指定的条件。处理默认存储和序列步骤存储之间的冲突时一定要谨慎。

虽然设置逻辑分析仪很困难,但触发函数可以大大降低此过程的难度。触发函数是可以组合起来设置触发的常用构建块。由于这些函数涵盖了大多数普通触发,因此通过选择适当的函数并将其填充到数据中即可设置触发。下图显示了逻辑分析仪触发用户界面。请注意,触发函数位于屏幕左侧的一个醒目位置。

图21 使用触发函数

通常,设置复杂触发的最大难题是对问题进行分解。换句话说,就是如何将复杂触发映射到序列步骤、分支和布尔逻辑表达式。

将问题分解为不同时发生的事件。这些事件对应于序列步骤。

扫描触发函数列表,尝试找出一些与步骤 1 中确定的事件相匹配的函数。

将所有剩余事件分解为布尔逻辑表达式及其相应操作。各个布尔逻辑表达式/操作对分别对应于序列步骤中的一个单独分支。请记住,可能存在只用于为序列步骤处理存储限定的“存储”分支。

设置逻辑分析仪触发与编写软件大相径庭。如果使用预定义的触发函数和较早编写的文档完善的触发来完成其他工作,就可大大降低设置逻辑分析仪触发的难度。仅在没有其他可用的资源时,才需要编写自己的触发设置。最后,当设置较难的触发时,可将问题分解为若干较小的部分,然后逐个解决。

逻辑分析仪探头

逻辑分析仪的探头是逻辑分析仪非常重要的一部分。因为逻辑分析仪主要用于在线测量,探头提供了与被测件的电气和机械连接,当我们选择探头时,这两个方面都是主要考虑因素。

如下图所示,探头被动的观察目标信号,目标信号的一小部分进入探头,通过互连线缆传递到逻辑分析仪模块,逻辑分析仪模块里面的放大器把这一小部分信号放大,还原原始波形。

探头的电气性能主要考虑2个方面,这与示波器探头的考虑因素是一致的。

1)不要干扰目标信号(探头的信号完整性)

2)模块内能够较精确的复现被测信号(探头的信号保真度)

图22 逻辑分析仪的探测

探头的结构细分下来也是比较复杂的。探头与被测传输线接触的小互连部分,可以使用PCB走线的方式,也可以使用导线,连接器或弹簧片,要根据实际情况选择。探头的前端包含电阻,有的是分立的SMT电阻,有的是分立电阻,一般阻值都在20k欧姆左右。探头前端到模块有长的电缆,已达到便于连接远近目标的方便性,这些电缆可使用同轴方式或使用双绞线方式,但都要保证足够的带宽。逻辑分析仪模块需要对电缆的阻抗进行匹配,防止传递过来的信号反射回去,还要对信号进行放大,因为传递过来的信号幅度比较小。

图23 探头的信号完整性考虑

探头的负载效应主要分为两种类型:直流负载和交流负载。

直流负载:探头看起来象一个对地的直流负载,一般是20K欧姆。如果被测总线具有弱上拉或弱下拉特性(即上下拉电阻较大),这个负载可能会导致逻辑错误。直流负载主要由探头尖的电阻决定,这个电阻阻值越大,直流负载越小,阻值越小,直流负载越大。

交流负载:探头包含寄生电容和电感。这些寄生参数会减小探头带宽和导致信号反射。我们需要在被测电路接收端和探头尖处考虑信号完整性。

探头带宽被降低主要来自2个方面:探头电容和探头与目标连接的连线的电容。

探头导致信号反射的原因是4个方面:探头电容和电感;探头在被测总线上的探测位置;总线的拓扑结构;探头和目标间连线的长度。

对于交流负载,我们需要考虑:探测点在传输线的位置,总线的拓扑结构和探头和目标间连线的长度。

探头的负载除了可以用复杂的Spice模型仿真分析外,也可以用简单的RC模型简单预估负载效应。下图是典型探头的RC模型。

图24 常用探头的RC模型

我们需要仔细考虑探头和目标之间的连线。为了可靠的电气连接,有三种方式可选择:短线探测(StubProbing),阻尼电阻探测(Damped Resistor Probing),电阻匹配探测(Resistive DividerProbing)。

短线探测会增加电容负载。举例:探头电容负载是0.7pF,连接短线是50欧姆微带线(C=3pF/in),长度1英寸。则整个探头的电容负载是3.7pF,这个短线是电容负载的主要部分。

被测系统可容忍的负载电容是多少呢?需要参考被测电路的系统上升时间,一般规则:短线的电气长度<系统上升时间的20%。一个允许短线长度的计算例子:

PCB传输延迟:150ps/in

系统上升时间:500ps

则最大电气长度:0.2x500ps=100ps

则最大短线长度:(100ps)/(150ps/in)=0.67in。

如果没法减小短线长度,可以试着用阻尼电阻探测的方式。阻尼电阻有2个作用:隔离来自短线的电容,消减来自短线的反射。

图25 阻尼电阻探测方式

阻尼电阻阻值大小的一般规则:目标阻抗的2.5倍。

如果探测环境需要更长的连线,这时候可考虑电阻匹配探测,即在探头尖处附加一个匹配电阻,消除连线的反射。匹配电阻的阻值与连线传输线的阻抗一样即可,但需要考虑信号的衰减。

图26 电阻匹配探测方式

逻辑分析仪的探头主要有3种类型:提前设计型;事后考虑型;定制型。

图27 逻辑分析仪的探头类型

小结:逻辑分析仪探头是逻辑分析仪非常重要的部分,典型探头的形状,连接,参数如下图所示。

图28 逻辑分析仪探头具体形状和参数

参考文献

[1] Agilent Technologies,Inc. Logic Analyzer HelpSystem[G/DK].Santa Clara:Agilent Technologies,Inc.2012.

[2] Agilent Technologies,Inc.Logic Analyzer ProbingChallenges,Considerations,and Options[R/DK].Santa Clara:AgilentTechnologies,Inc.2010.

[3] Agilent Techlologies,Inc.Logic AnayzerBasic[G/DK].Santa Clara:Agilent Technologies,Inc.2008.

爱华网

爱华网