数字逻辑,是数字电路逻辑设计的简称,其内容是应用数字电路进行数字系统逻辑设计。电子数字计算机是由具有各种逻辑功能的逻辑部件组成的,这些逻辑部件按其结构可分为组合逻辑电路和时序逻辑电路。组合逻辑电路是由与门、或门和非门等门电路组合形成的逻辑电路;时序逻辑电路是由触发器和门电路组成的具有记忆能力的逻辑电路。有了组合逻辑电路和时序逻辑电路,再进行合理的设计和安排,就可以表示和实现布尔代数的基本运算。

数字逻辑_数字逻辑 -数字逻辑

数字逻辑_数字逻辑 -正文

主要用以研究有两个离散状态的开关器件所构成的数字电路。能对电路的输入与输出之间的关系提供理想描述,研究这种描述的特性和电路的实现,并探讨将数字电路或数字模块互连起来完成特定逻辑功能的理论和方法。具有两个或多个离散状态的开关器件或单元是:可断开和闭合的开关或继电器的触点;能正偏和反偏的整流二极管;能饱和和截止的开关电子管或开关晶体管;能在两个饱和方向中任意一个方向上磁化的磁心。具有二个离散状态的开关器件是最常见的。数字逻辑不考虑特殊条件下动作或稳定的物理现象和从一个状态过渡到另一个状态的细节。数字逻辑的部分理论建立在数理逻辑,特别是布尔代数和时序机的理论基础上。

数字逻辑可分为组合逻辑和时序逻辑。在一个逻辑系统中,输出结果仅取决于当前各输入值的称组合逻辑;输出结果既由当前各输入值,又由过去的输入值来决定的称时序逻辑。组合逻辑不包含存储元件,时序逻辑至少包含一个存储元件。

数字逻辑的应用范围极广,日常生活的决策过程是组合逻辑的典型例子。电话号码的拨号和号码锁的开启过程,则是时序逻辑的典型例子。数字逻辑在数字电路设计中有广泛的用途。

组合逻辑组合逻辑的输出由其输入确定的法则,通常称为开关函数。因为变量是离散的,一个开关函数可以用表格形式的真值表来表示,也可以用各种图来表示。如果函数和变量是二进制的,符号“1”和“0”通常用来表示这两个值。这样的函数能用二元布尔代数表达式来描述,称开关函数。开关函数的二个数值,可以对应开和关,或继电器触点的闭合和开启;可以对应电子电路电压的高与低,或正和负;也可以对应逻辑真和假。

最简单的开关函数是“非“函数、“与“函数和“或“函数。“非”函数表示为布尔非:Y=

,意即X为假,Y为真。“与”函数表示为布尔乘:Z=X・Y,意即仅当X・Y皆真,Z才真。“或”函数表示为布尔加:Z=X+Y,意即X或Y中任意一个为真,Z即为真。若用“1”表示逻辑“真”,“0”表示逻辑“假”,上述三个基本开关函数符合如下布尔代数法则:

=10・0=00+0=0

=00・1=00+1=1

1・0=0 1+0=1

1・1=0 1+1=1

将这些基本逻辑单元加以组合,可以构成其他所有组合逻辑。这种逻辑可以根据输入变量的真、假组合来确定输出的真、假。因此,组合逻辑是一种决策逻辑,它可能十分简单,也可能异常复杂。这些决策是需要某些逻辑数学方面的知识,也需要使用某些工具,如真值表、布尔代数、符号逻辑和波形等。

真值表这是用真、假值来表示输入逻辑变量与输出开关函数之间关系的表格。它由两部分组成,左边一栏罗列输入变量的各种可能取值,一般按大小顺序排列。右边一栏是与各输入变量取值相对应的函数取值。表1是一位全加器的真值表。X、Y、Z分别表示加数、被加数和低位的进位。S和C分别表示和以及本位进位。

数字逻辑函数式输出结果与输入变量之间的开关函数关系,还可用布尔表达式来描述。对应于表1中一位全加器的布尔函数式为

S=

・

・Z+

・Y・

+X・

・

+X・Y・Z(1)

C=X・

・Z+X・Y・

+X・Y・Z+

・Y・Z(2)

一个开关函数可用多种形式的布尔表达式来描述,每种表达式对应一种逻辑电路。但是,开关函数的标准布尔表达式却具有唯一性,它与真值表有严格对应关系。标准布尔表达式有两种:最小项标准式和最大项标准式。最小项标准式包含所有变量的乘积项,又称全积项,它由真值表中函数的“1”值推出,式(1)、(2)为一位全加器的最小项标准式最大项标准式。包含所有变量的和式,它由真值表中函数的“0”值推得,上例函数最大项标准式为

=(

+

+

)・(

+Y+Z)・(X+

+Z)・(X+Y+

) (3)

=(

+

+

)・(

+

+

)・(

+Y+

)・(X+

+

) (4)

卡诺图卡诺图是一种平面方格图,每个方格代表标准函数中的一个最小项。方格的布局是按相邻项和的对折原理安排的,能清楚地表现其相邻关系。卡诺图是利用这种相邻关系,合并最小项消去一些项来化简函数的。图1是式(2)三个变量的卡诺图。

数字逻辑从图中可以直观地看出公式(2)可简化成

C=XY+XZ+YZ(5)

利用卡诺图的方法可以化简具有1个输出和多到6个输入的函数。当输入变量增多时,函数可能的组合将非线性地迅速增长。另一方面,随着微电子技术的发展,逻辑的规整性具有更重要的意义,因而函数优化的目标也有所改变。

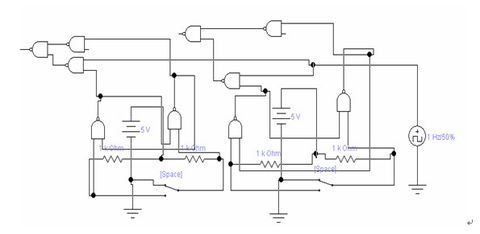

图2是根据式(1)、(5)绘出的一位全加器的“与”“或”门电路图。

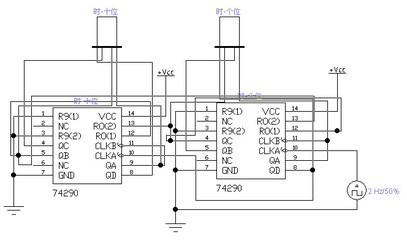

数字逻辑时序逻辑因为时序逻辑的输出不仅依赖于当前的,还依赖于过去的输入,它们必须包含有维持继电器、触发器、延迟线或者磁心等记忆或存储过去输入状态的元件。有两个稳定状态的元件能记忆一个二进制数或位。电路的记忆量可用位数或内部状态数来确定。一个电路的内部状态取决于内部记忆元件中的构造,当n表示位数时,内部状态数不超过2n。二进制计数器、移位寄存器和各类触发器都是时序电路的例子。

时序逻辑可表示为有反馈的组合逻辑,图3是时序逻辑的一般表示。其中:xi、zi、Mj和mj

分别称为输入变量、输出变量、状态变量和次态变量。对时序逻辑,需要用两组方程才能完整地描述其特性:

数字逻辑zi=gl(x1,…,xn,M1,…,Ml)(6)

i=1,2,…,k

mj=fj(x1,…,xn,M1,…,Ml) (7)

j=1,2,…,l

关系式(6)表示,每个输出变量zi是当前输入变量和状态变量的布尔函数gi,gi称为输出函数。关系式(7)表示,次态变量(即下一个时刻的状态变量)。可由当前输入和状态作自变量的布尔函数fj计算出来,fj称为转换函数。对时序逻辑,这些变量值通常在一些不连续的瞬间取样。在进行下一次计算前,次态变量被存入存储元件,作为新的状态变量。

分类用一个专门的定时信号作输入(称为“时钟“)对状态变量进行瞬间取样来控制时序逻辑电路的动作,称为“同步“时序电路。没有专门定时信号的,称为“异步”时序电路。同步时序电路的每个状态都是稳定态,只有异步时序逻辑才有不稳定态。

竞争与冒险以上论述的都是输入和输出稳定状态之间的理想关系,没有考虑电路实现中信号经过电路和导线的延迟和延迟时间的不均匀性。实际上,仅考虑理想的稳态解是不够的,还必须研究过渡过程或暂态解。在数字逻辑电路的设计中常用竞争和冒险来分析过渡过程。所谓竞争,是指电路在瞬态过程中存在着一个以上的不稳定状态变量。若电路所趋向的最终稳定状态与状态变量的变化次序有关,则称电路的竞争是临界的。否则,电路的竞争是非临界的。临界竞争会使电路的输出结果不确定。为了消除竞争,可以在组合电路中插入可控制的延迟,或者通过适当的状态赋值来消除临界竞争。

冒险在组合电路和时序电路中都可能发生,但只对时序电路有严重影响。在一对相邻输入状态的转换过程中,可能导致电路的瞬间错误输出,这种转换过程称冒险。为了消除冒险,可在次态变量的反馈环路中插入延迟单元,使输入变量的变化完成后,再使状态变量发生变化。

状态表和状态图正如组合逻辑可用真值表、函数式和卡诺图等几种形式来表示,时序逻辑可用状态表和状态图来描述。状态图通常由状态表推出,更直观易读,一般作为时序逻辑的原始设计规范。状态图用圆表示一个状态,圆中的二进制数字表示这个圆所处的状态。用连接圆的有向线表示状态间的转换。有向线上有两个二进制数字,用“1”线割开,前者表示导致状态转换的输入条件,后者指当前状态下的输出值。连接同一个圆的有向线表示状态不变。状态图和状态表提供同样信息。图4a是一个带有一位全加器的逻辑图,图4b和表2是它的状态图和状态表。

数字逻辑

数字逻辑参考书目

Raymond E.Miller,Switching Theory,Wiley, New York,1979.

Samuel C.Lee,Modern Switching Theory and Digital Design,Prentice Hall, Englewood Cliffs,New Jersey.,1978.

Fredrick J. Hill,and Gerald R.Peterson,Introduction to SwitchingTheoryand logical Design,2nd ed.,Wiley,New York,1974.

数字逻辑_数字逻辑 -配图

数字逻辑_数字逻辑 -相关连接

爱华网

爱华网